从零开始的DFT工程师!

为什么要开始这个系列

开始做这个系列其实还是想要多学一点东西,感觉自己会的还是太少了,完全没有一个正常水平的数字集成电路应届毕业生的水平。而且其实差不多从大三上学期开始后我就状态低迷了一整年

现在的想法是这样的:这个学期选了自然辩证法(前八周)和集成电路前沿讲座(后八周),都是我们学校研究生的课,先多学一点,这样可以省下研一上学期的一点时间,然后多做点东西;尽早招老师开个题,毕设最好是前八周学学基础知识然后就开始做,寒假做完,在大四下学期找找实习,如果能找到的话就出去实习一个学期,找不到的话就选新中特和半导体器件这些课,给研究生在多一点时间,总体来说就是想多学一点。

我的计划是?

我计划面向实习为主,希望实习可以找一个自己喜欢的方向去做,目前觉得比较想去的就是AI处理器验证,DFT DV Engineer这个方向(其实是因为好找实习),然后也多学一些GPU图形化驱动方面的coding.

AI 处理器验证和DFT DV Engineer

- AI 处理器验证:主要负责验证功能是否正确,保证在tapeout前没有设计缺陷。

芯片验证主流的方法学是UVM(Universal Verification Methodology),他提供了一套标准化的框架和库,可以用来搭建验证环境,生成激励,并进行全面的功能覆盖。

当然有时工作还包含Post-silicon debug,芯片造出来以后发现功能不正确是就要进行流片后调试,定位并分析问题。

对于SoC验证当然需要在多了解一些总线相关知识,这个似乎比较繁杂,尽量多了解一些就可以了。

- DFT DV Engineer:Design For Test, Device Verification.

在芯片设计中提前加入特殊电路以便于在芯片制造和测试阶段高效全面的发现制造缺陷。

感觉内容比较多就不在这里写了

GPU C++ modeling

这一项属于架构探索和设计前期的工作,主要职责是构建一个高性能高精度的GPU行为级模型(感觉上来讲比前两个难一些,本科生实习也难找)。

其内容多数应该是用C++完成行为级(或以上)的软件模型构建,应该需要对体系结构,并发/超前等内容有所了解。

预计应该学习的内容

验证基础

systemverilog: testbench, interface, assertion.

UVM: verification environment, sequence, driver, monitor, coverage.

verify process: testplan -> testcase -> coverage analysis -> find bug.

SoC verification: AMBA bus(AXI,AHB,APB), peripherals.

DFT

scan chain.

ATPG.

JTAG, Boundary scan.

MBIST(memory build in itself test).

ATE bring-up.

shmoo.

screenplay

python, shell, perl.

硬件调试

FPGA/Emulator: vivado/Quartus.

Post-silicon bring-up.

GPU C++ modeling

CPU/GPU pipeline.

trace-driven/execution-driven.

并行/超前计算,SIMD, shader.

software using

verification tools

emulator: synopsys VCS / Mentor Questasim / cadence xcelium.

debugger: verdi(waveform?)

formal verification: JasperGold.

DFT tools

synopsys TetraMAX(ATPG).

DFT compiler.

mentor tessent.

design/analysis tools

design compiler, primetime, powerartist/PTPX.

GPU modeling tools.

gem5, GPGPU-sim.

学习计划

此处写一个学习路线,供参考。

| week | content | link | tools |

|---|---|---|---|

| 1 | verilog+systemverilog | week 1 | verilog: iverilog + gtkwave vivado systemverilog: cadence virtuoso + simvision + incisive slang + UHDM + surlog + yosys + verilator |

| 2 | makefile/python + tcl/cmake/jenkins | week 2 | makefile/cmake/python/tcl |

| 3 | EDA&UVM foundation | week 3 | systemverilog/synopsys |

| 4 | EDA&UVM foundation part.2. | week 4 | systemverilog/synopsys |

| 5 | systemC foundation | week 5 | C++/systemC |

| 5 | Assertions &Coverage SVA, functional coverage |

week 5 | verilog + systemverilog |

| 6 | auto UVM test python/makefile/git… |

week6 | python/tcl/makefile/git |

| 7 | AI accelerator pipeline/hazard/stall/forwarding |

week 7 | verilog+systemverilog |

| 8 | systolic array | week8 | verilog + systemverilog |

| 9 | AI accelerator verification: systolic array |

week 9 | verilog + python + golden model |

| *10 | log parser python + coverage + analysis -> HTML report |

week10 | python + systemverilog + UVM + synopsys |

| 11 | verification: scan chain/MBIST/JTAG/Boundary scan low power verification: UPF/CPF/clock gating/power gating |

week 11 | none |

| 12 | RTL2FDSII mention:verification architecture cocotb/UVM-lite |

week 12 | none |

| 特别篇1 | synopsys 工具组的安装 | synopsys install | none |

| 特别篇2 | systemverilog | sv&vcs | systemverilog vcs |

| 特别篇3 | 远程连接 | server | nope |

| spe.1. | GPU C++/CUDA kernel/memory/hierarchy |

spe.1. | CUDA Toolkit + Nsight |

| spe.2. | GPU C++ project contain shared memory optimization |

spe.2. | CUDA Toolkit |

| spe.3. | GPU C++ performance modeling and analysis | spe.3. | modeling: GPGPU-sim gem5-gpu Accelsim analysis: NVIDIA Nsight Compute Nsight Systems |

| spe.4. | graphic foundation: OpenGL/DirectX Vulkan GPU SIMT |

spe.4. | none |

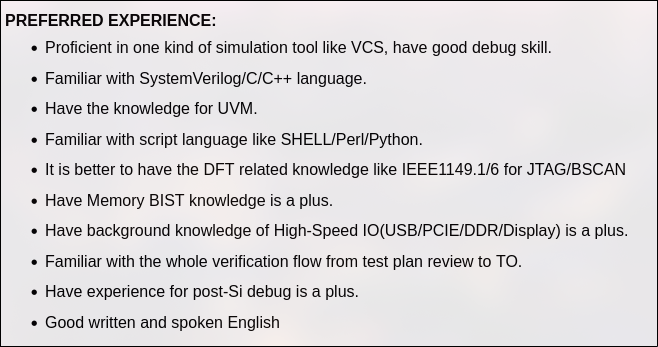

此处我展示一个DFT工程师招聘要求:

使用AI工具是很重要的

在学习的过程中一定要好好使用AI工具,而且前提是好用的AI工具(来自我的导师,误)。那么我们有时需要和他人合买(或者纯粹出于某些原因需要)使用API连接,这里直接安利一个个人感觉很不错的小工具,anythingllm。

有一个官方的desktop 下载链接

还有一个docker方式使用也很简单(但是docker的网络配置是有点坑在里面的,可以尝试一下突破技术壁垒),只需要下载docker镜像:

1 | docker pull mintplexlabs/anythingllm |

然后自己创建一个用于存放信息的目录,比如/home/user/anythingllm,创建一个.env文件比如/home/user/anythingllm/.env

之后直接运行:

1 | docker run -d -p host_port:container_port \ |

就开启了anythingllm环境,当然我们也可以图简单:

1 | echo 'anythingllm="docker run -d -p <host_port>:<container_port> --cap-add SYS_ADMIN -v /home/user/anythingllm/:/app/server/storage -v /home/user/anythingllm/.env:/app/server/.env -e STORAGE_DIR="/app/server/storage" -e HTTP_PROXY=http://<host_ip>:<host_proxy_port> -e HTTPS_PROXY=http://<host_ip>:<host_proxy_port> -e NO_PROXY=localhost,127.0.0.1 mintplexlabs/anythingllm:latest"' >> /home/user/.bashrc |

一般写两个端口相同。

之后就可以直接通过anythingllm打开,如下:

在浏览器中输入localhost:port就可以进入界面。

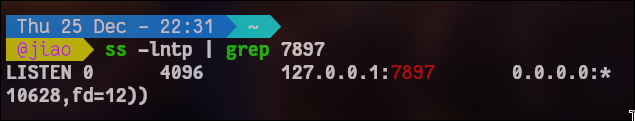

如果出现网络问题,可以测试ss -lntp | grep <host_proxy_port>,如果结果是127.0.0.1:<host_proxy_port>,那就会连不上,如下:

这种情况大多是设置问题,总的来说需要修改如下设置:

- mixed-port:xxxx

- bind-address:0.0.0.0

- allow-lan: true (这个是允许通过LAN连接,必须打开)

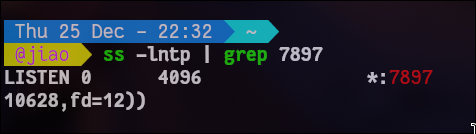

之后在测试,结果如下:

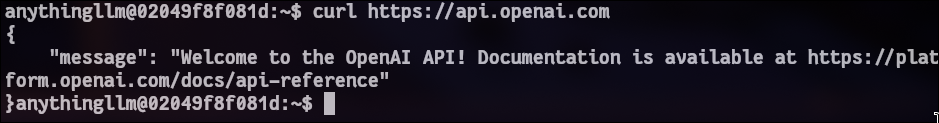

在container中的测试:

或者可以通过一下方式绕过nodejs:

1 | docker run -d -p 3001:3001 --name anythingllm --network host --cap-add SYS_ADMIN -v /home/jiao/anythingllm/:/app/server/storage -v /home/jiao/anythingllm/.env:/app/server/.env -e STORAGE_DIR=/app/server/storage -e HTTP_PROXY=http://127.0.0.1:7897 -e HTTPS_PROXY=http://127.0.0.1:7897 -e NO_PROXY=localhost,127.0.0.1 -e NODE_TLS_REJECT_UNAUTHORIZED=0 mintplexlabs/anythingllm:latest |